Motivation

1 / 12

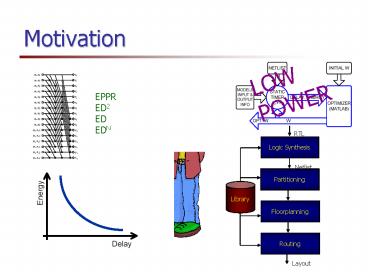

Title: Motivation

1

Motivation

LOW POWER

EPPR ED2 ED EDN

2

Problem Statement

- Incorporate E-D sensitivity analysis using an

appropriate metric into logic synthesis to

produce designs optimized in the energy-delay

space. Success of implementation is measured by

two parameters - Rate of convergence (RoC) of results

- Implementation must produce results fast

- Quality of result (QoR)

- Results should be equivalent to custom-design

3

Prior Work

GUIDING PRINCIPLE At all levels of design,

balance energy-to-delay sensitivity of each

tuning variable similarly.

- R.W. Brodersen, M.A. Horowitz, D. Markovic, B.

Nikolic, V. Stojanovic. Methods for true power

minimization. IEEE/ACM International Conference

on Computer Aided Design. IEEE/ACM Digest of

Technical Papers. IEEE. 2002, pp.35-42.

Piscataway, NJ, USA. - R. Zlatanovici, B. Nikolic. Power - Performance

Optimal 64-bit Carry-Lookahead Adders, European

Solid State Circuits Conference (ESSCIRC) 16-18

September 2003, Estoril, Portugal, pp. 321-324

4

Investigative Approach

- Build and test synthesis-based front-end and

back-end design flow - BWRC BEE front-end and ST Avanti-based back-end

- Evaluate E-D sensitivity metrics for accuracy and

simplicity - Metrics Cgate/Cwire, EPPR, ED

- Benchmarks with known logic and wire structure

- Evaluate relative impact of wiring on power

density for hierarchical designs vis-à-vis sizing - Create models and simplified sensitivity analysis

tool appropriate for synthesis embed into design

flow - Test on real-world benchmarks

- Evaluate results based on RoC and QoR

5

Conventional Methodology

RTL

No accurate models for energy-delay tradeoffs. Ad

-hoc decisions to meet power budget

Logic Synthesis

Netlist

Power- Performance OK?

No

Library

No

Yes

Power- Performance OK?

Place Route

Layout

Yes

6

BWRC Front-End Flow

Matlab/Simulink

Test Vectors

Xilinx System Generator

High Level Models

Environment Setup

Behavioral VHDL

Design Flow Management

P R Constraint Files

Synopsys PrimeTime

Synopsys Design Compiler

DC Scripts

Gate-level VHDL

P R Constraints

7

Hand-Off To Back-End

ST Unicad Setup

Handoff Avanti Setup

Files Placed In Directories

Environment Setup

Handoff Scripts

HO Generate Tasks

Clock Tree Defn. Scripts

CT Generate Tasks

Clock Constraints

CT Edit

Power Supply Specification

Power .attx file

Netlist Checks

8

Avanti Back-End Flow Summary

9

Proposed Design Flow Changes

The key is in selecting an accurate but

simpleE-D sensitivity metric

RTL

Model is topology-dependent

Logic Synthesis

Power-Performance Optimization Using E-D

Sensitivity Analysis

Data must be in a uniform format to allow tight

integration fast computation

Library

Place Route

Model is interconnect and gate-size dependent

Layout

10

Preliminary Results

11

Preliminary Results

12

Future Work

- Complete evaluation of impact of wiring on power

density and delay for IEU - Relate to EPPR and choice of Cin

- Evaluate EPPR vs. Cwire/Cgate ratio for ALU and

IEU - Refine models for energy, delay, sensitivity

- Incorporate into synthesis tool

- Evaluate on real-world example

- Measure RoC and QoR