Assembly Code - PowerPoint PPT Presentation

1 / 16

Title:

Assembly Code

Description:

HW 2 out today (check the course web site) CS 141 Chien April 16, 1999 ... update a register as part of load (for marching through arrays) ... – PowerPoint PPT presentation

Number of Views:45

Avg rating:3.0/5.0

Title: Assembly Code

1

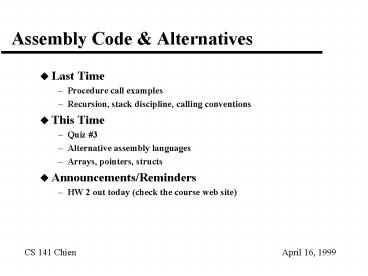

Assembly Code Alternatives

- Last Time

- Procedure call examples

- Recursion, stack discipline, calling conventions

- This Time

- Quiz 3

- Alternative assembly languages

- Arrays, pointers, structs

- Announcements/Reminders

- HW 2 out today (check the course web site)

2

Full MIPS Calling Conventions

- 0 Constant 0

- AT 1 Reserved for Asm and OS

- v0-v1 2-3 Return Values

- a0-a3 4-7 Arguments

- t0-t9 8-16,24,25 Caller saved Registers

- s0-s7 16-23 Callee saved Registers

- k0-k1 26-27 Reserved for Asm and OS

- gp 28 Global Pointer

- sp 29 Stack Pointer

- fp 30 Frame Pointer (base of stack frame)

- 31 Return address from jal

3

Perspective on the MIPS Instruction Set

- definitely a RISC Reduced Instruction Set

Computer - Instructions are simple and regular

- There are only a modest number of operation codes

- There are VERY few addressing modes

(displacement, some PC-relative) - Instructions are all the same size

- A few fixed formats for the instructions

- One of the original academic RISC projects that

went commercial... (the other is the SPARC -- Sun

architecture)

4

Assembly Overview for MIPS architecture

- Approximately....

- 40 Add class opcodes

- 20 control transfer (Jump and Branch)

- 25 memory instructions

- 25 Floating point instructions

- 5 miscellaneous

- gt still nearly 150 instructions

- 3 formats, all 32 bits

- only 2 addressing modes

- 32 general purpose registers

5

MIPS Overview (cont.)

- gt Most of these features aid the implementation

(fast, simple) - Simple instruction sets are good for exposition

of the minimal functionality required. - gt Not all instruction sets are this way...

- Why?

- Simple parametric choices

- Evolution and learning how to do things better.

- Previously, lots of assembly code was written by

programmers, so focus on providing higher level

interfaces

6

MIPS ISA Tradeoffs

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

OP

rs

rd

sa

funct

rt

OP

rs

rt

immediate

OP

target

- What if?

- 64 registers

- 20-bit immediates

- 4 operand instruction (e.g. Y AX B)

7

Significant Design Points

- 80x86 -- most popular processor (32 and 64 bit)

- PowerPC -- commercial RISC architecture

- VaX -- commercial CISC architecture

- Design alternative

- provide more powerful operations

- goal is to reduce number of instructions executed

- danger is a slower cycle time and/or a higher CPI

- Sometimes referred to as RISC vs. CISC

- virtually all new instruction sets since 1982

have been RISC - VAX minimize code size, make assembly language

easy instructions from 1 to 54 bytes long! - Well look at 80x86, PowerPC, VAX

8

80x86

- 1976-8 Intel 8080/8085

- 1978 The Intel 8086 is announced (16 bit

architecture) - 1980 The 8087 floating point coprocessor is

added - 1982 The 80286 increases address space to 24

bits, instructions - 1985 The 80386 extends to 32 bits, new

addressing modes - 1989-1995 The 80486, Pentium, Pentium Pro add a

few instructions (mostly designed for higher

performance) - 1997 MMX is added

- 1999 Katmai (Streaming SIMD extension -SSE)

9

80x86 (cont.)

- How instructions were chosen, very strict

limitations - Memory constraints

- Registers data (8) and address (segment 6)

- 8,16,32-bit instructions (compatibility)

- 2-address instruction set

- add r1,r2

- range of instruction formats, and instruction

lengths - Instructions from 1 to 17 bytes long

- one operand must act as both a source and

destination - one operand can come from memory

- complex addressing modes e.g., base or scaled

index with 8 or 32 bit displacement

10

80x86 (cont. 2)

- prefixes as an extension of formats

- built-in procedure call and return instructions

- Ex 9 ways to clear a register

- Saving grace

- the most frequently used instructions are not too

difficult to build - compilers avoid the portions of the architecture

that are slow - But, not really complex, due to chip size limits.

- See your textbook for a more detailed description

11

PowerPC

- Indexed addressing

- example lw t1,a0s3 t1Memorya0s3

- What do we have to do in MIPS?

- Update addressing

- update a register as part of load (for marching

through arrays) - examplelwu t0,4(s3) t0Memorys34s3s3

4 - What do we have to do in MIPS?

- Others

- a special counter register bc Loop

- decrement counter, if not 0 goto loop

12

Key Points

- MIPS is a general-purpose register, load-store,

fixed-instruction-length architecture. - MIPS is optimized for fast pipelined performance,

not for low instruction count - Four principles of IS architecture

- simplicity favors regularity

- smaller is faster

- good design demands compromise

- make the common case fast

13

A Modern Alternative the IBM/Motorola PowerPC

Architecture

- Designed 1989 / 1993

- Leverages RISC ideas

- 32 general purpose registers, segment registers

for larger address space - simple instruction set, few compound operations

added for critical inner loop operations - autoincrement/decrement modes

- multiply/accumulate

- branch architecture condition codes, multiple

sets, separate test and use of information,

distinct namespace - Designed for multiple issue, a modern RISC?

- All of these machines are getting quite complex.

14

A high-end design point DEC VAX

- VAX (Virtual Address Extension)

- 11/730-780, 1978-1987

- 8xxx series, 1988 - present, 16 data registers, a

few special - Orthogonal Architectures -gt opcodes and all

addressing modes - Many operations 250, many addressing modes (8),

all possible combinations, hardware must deal

with these - Many formats, alignment of fields dependent on

the addressing modes - Complex operations like polynomial evaluate,

block move - Special call/return instructions

- Execution time from 5 - 5,000 cycles, extremely

complex implementations - Wulf subsetting argument, compilers

15

What is RISC vs. CISC?

- Debate about instruction set complexity

- Mostly over, since compilers deal best with

simple instruction sets, and eases

implementation, everyone subscribes. - Many shades of grey in RISC iness

- Most implementations are extremely complex (5M to

50M transistors) - Simple implementation is not a strong argument

- Ability to achieve high clock speed, high

performance is the major motivation now.

16

Summary

- Alternatives in instruction set architecture

- Driven by programming and implementation issues

- Can see the programming issues

- Will explore implementation issues in second

third of the class